Due: Saturday, July 20 at 11:59PM

Submission: On Courseworks

Complete the following assignment and submit on courseworks in either doc, docx, or pdf format. If you complete the assignment on pen/paper, please create a word or pdf document using clear images or scans of your physical copy.

Implement an OR gate using only a two-input mux and constant inputs (in addition to inputs A and B)

We construct the following circuit representing a game. Our circuit has the following inputs:

For C==1, the output (called f) is 1 if P0 and P1 are equal (P0 == P1 == 1 or P0 == P1 == 0), and 0 if not (P0 != P1). For C==0, the output is 1 if P0 and P1 are not equal and 0 if they are (e.g. the reverse behavior of C==1).

Implement the following:

Show how to implement

f = X̅ Y̅ Z + Y Z̅ + X Y̅

using:

Draw a circuit for an eight input mux using three four-input muxes and no other gates.

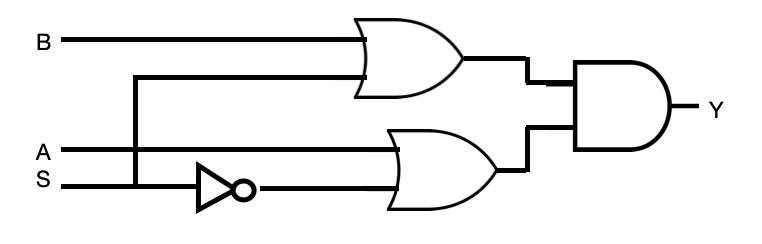

Consider the following circuit:

Under what conditions could the output of this circuit glitch high? I.e. for what assignment of input values would changing one input’s value cause the output to briefly transition from 0 to 1 to 0? Modify the circuit (add or change gates and wires) so it computes the same function but cannot glitch in this situation.

Implement a three-bit binary carry-lookahead adder. Its inputs are A0,…,A2 and B0,…,B2 for the two addends, and C0 for the carry in. Its outputs are Y0,…,Y3

G0,…,G2 and P0,…,P2, the carry generate and propogate functions, in terms of the inputs.C1,…,C3 in terms of the G’s, P’s, and C0Y’s (use “⊕” for XOR)AND, NAND, OR, NOR, and XOR gates with as many inputs as you’d like. The critical path should be four gates. Please be neat.