# Pitch Perfect: A Hardware-Accelerated Real-Time Phase Vocoder for Pitch Scaling

Embedded Systems Design (CSEE4840)

Spring 2024

Sanjay Rajasekharan (sr3764), Maria Rice (mhr2154), Steven Winnick (shw2139)

#### **Abstract**

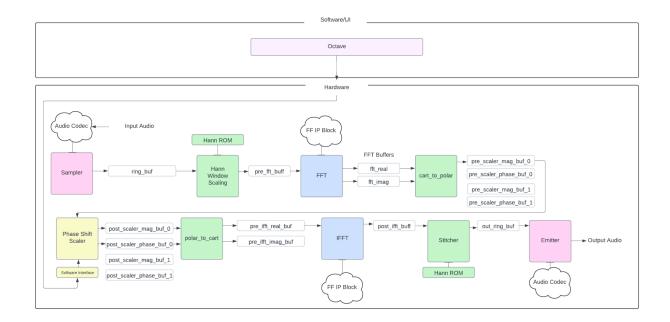

Our project aims to build a phase vocoder for real time pitch scaling primarily through hardware. We utilize an FFT block from the Intel IP Core to perform a Short Term Fourier Transform on the input audio stream. Combined with a series of other hardware-based transformations, further described below, the input audio stream will be pitched up or pitched down by a configurable amount.

# **Revised Proposal**

Our original inspiration for this project was to create a karaoke companion that allows users to hit high notes through live pitch shifting. Once we more deeply understood the complexities of creating a real-time phase vocoder, our focus shifted to doing just so, removing emphasis from both audio input and output.

In our final output, each of the components of the pitch shifter have been written and compiled to hardware, with the intention to test and execute the linked system on the DE1-SOC board. However, due to a variety of constraints including significant time spent debugging, the system does not work as a whole.

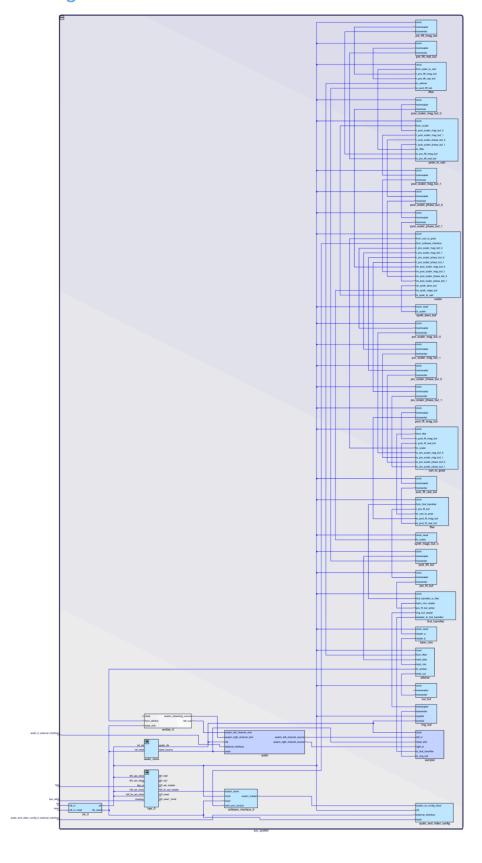

# **System Block Diagram**

# Algorithm Description: The Phase Vocoder Algorithm for Pitch Scaling Input

The algorithm takes as input a stream of audio. In our implementation, these samples are signed 16-bit integer values at a sample rate of 48kHz.

# Windowing

The input audio stream is then split into overlapping "windows," or groups of samples. Each window contains 4096 samples, and is offset by a "hop length" of 1024 samples from the previous window.

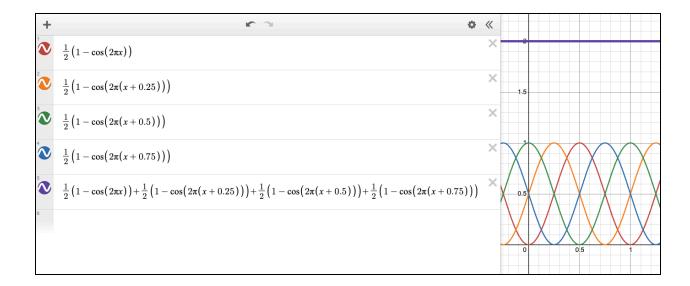

# First Hann Window Scaling

The samples in each window are then scaled according to the Hann Function, so the zero-indexed  $n^{\text{th}}$  sample in a window will be scaled by a factor of  $\sin^2(2\pi n/4095)$ . This does not cause a loss of information about the original audio stream. Because each window is offset by ¼ of the window length and for all n,

$$\sin^2(2\pi n) + \sin^2(2\pi(n+0.25)) + \sin^2(2\pi(n+0.5)) + \sin^2(2\pi(n+0.75)) = 2$$

we are able to reconstruct the original audio by adding half of each sample's windowed value for all 4 windows it appears in.

#### **Short-Time Fourier Transform**

A Fourier Transform is then applied to each scaled window. In our implementation, we use the polar coordinate representation of the complex values for more space-efficient computation in hardware.

# **Phase Shift Scaling**

This is the point in the algorithm where the pitch scaling actually occurs. For each frequency bin in a given window, we compare the difference in phase between the current and previous windows to the difference we'd expect from a pure tone (sine wave) at that bin's center frequency of *n* cycles per window, which gives it an expected phase difference of

$$2\pi n/(1024/4096) = \pi n/2$$

The gap between the expected and observed phase differences, wrapped to a value between  $-\pi$  and  $\pi$ , gives us a fractional "bin deviation" indicating how high up or down the real pitch captured by the bin was relative to the bin's center. We then scale the sum of this value and n by a constant factor, the pitch scaling amount, to determine the output "synthesis" bin for this sound. The amount that this differs from the whole-number bin number it is rounded to again gives us a bin deviation, but this time for the synthesized output bins. When multiple input bins end up scaled to the same output bin, we sum their bin deviation contributions. In a process that exactly mirrors the one on the input side, we compute a "phase remainder" using the fractional bin deviation, which tells us how much the actual phase difference of the bin from the previous window to the current one ought to differ from our expectation based on the bin's center frequency. We then add this, the expected phase difference, and the phase of the same bin in the prior window to get the new phase for the bin. For the magnitude, we use the sum of all the input bin magnitudes that ended up in the same synthesis bin.

#### **Inverse Fourier Transform**

After being converted back from polar to imaginary values, an inverse Fourier Transform will be done to each window to return it to an array of samples.

#### Second Hann Window Scaling

To minimize artifacts in the synthesized sound, we repeat the same Hann Function scaling a second time. This allows for a smoother blend between windows whose time-domain waveforms may now be discontinuous from one another.

# Window Stitching

The de-transformed phase-adjusted windows of samples are then stitched back together into a main audio stream by adding half of each sample's windowed value for all 4 windows it appears in.

#### Output

The algorithm outputs a stream of audio. Like the input, in our implementation these will be signed 16-bit integer values at a sample rate of 48kHz.

# **Preliminary Software Implementation and Simulation**

# Python File Converters

Utilizing another

# Python Algorithm Simulation

Initially, we attempted to implement our pitch scaler in C without any code reference that implemented our exact pitch-scaling algorithm. We had reference code for a <u>similar algorithm</u> we found from a <u>YouTube video</u> that claimed to work with pitch scaling but only included code for time stretching. We attempted to implement this in C, adapting the code based on the logic in the video to perform pitch scaling instead of time stretching, but despite much time debugging, couldn't get it to work.

We then found another <u>video</u> on a related algorithm from a course at Queen Mary University of London, with <u>skeleton code</u> from a corresponding homework assignment to implement the algorithm in C++. This time, we decided to attempt the implementation in Python first, allowing us to limit variables relating to reading an input file and performing the Fourier Transform, which we were still in the process of testing in C, using SciPy and Librosa. We also used NumPy to abstract away details of the matrix operations done in the pitch scaling algorithm. Having this more abstract Python simulation allowed us to easily fine-tune details of our algorithm, such as the window size and hop length, before implementing them in C.

#### C Real-Time Streaming Algorithm

The next step was to create a slightly modified version of our outer-level C program which could be used to test our algorithm in "real time," allowing it to process a stream of input audio of any length and output a stream of pitch-scaled audio as it ran. Our simulation worked by reading samples from the standard input and emitting the scaled stream to the standard output, which would allow it to connect to programs to stream live audio to it and playback its output as live audio. For our testing, however, we would simply pipe in a long sequence of samples from a file and output them to another file, which we would then convert to a listenable format.

#### C Fourier Transform

Our Fourier Transform functions in C were created based off of various implementations found online. The transform consists of 3 main functions:

```

void rearrange (float real[], float imaginary[], const unsigned int N); This function is crucial for preparing data before applying the FFT algorithm. Its purpose is to reorder the real and imaginary parts of the complex numbers so that the FFT computation may be applied more efficiently. It does so using a bit-reversal method, reordering the elements of an array so that their indices are reversed in binary representation.

```

```

void compute (float real[], float imaginary[], const unsigned int N); This function performs the core FFT computation on the inputted complex numbers. It iteratively computes the FFT by dividing the input data into smaller groups and applying twiddle factors to combine them, following the Cooley-Tukey FFT algorithm. The Cooley-Tukey FFT algorithm is a commonly used method which breaks down FFT computation into smaller subproblems, applying a divide-and-conquer approach, to efficiently compute the FFT.

```

```

void inverseCompute(float real[], float imaginary[], const unsigned int N); This function computes the inverse FFT of the given complex numbers. It first conjugates the data before calling both rearrange() and compute() in order to perform a forward FFT on the data. Lastly, it conjugates the results again to receive the inverse transform before scaling the result by 1/N in order to get the correct inverse FFT output.

```

Both the forward and inverse FFT were tested on a variety of data points, including a window size of 4096 which is its ultimate application within the phase vocoder algorithm.

#### Shell Script

A simple shell script that creates an end to end pipeline for the software simulation. Sets up a python environment with the necessary requirements for WAV file processing. It then runs the

python converter script and stores the WAV samples in a temporary file. It then iteratively pipes these samples into the C vocoder algorithm, storing this next step of the output in a new temporary file. Finally, the TXT to WAV python script is run on the output of the vocoder, generating a pitched audio file while removing all intermediate files.

# **Hardware Implementation**

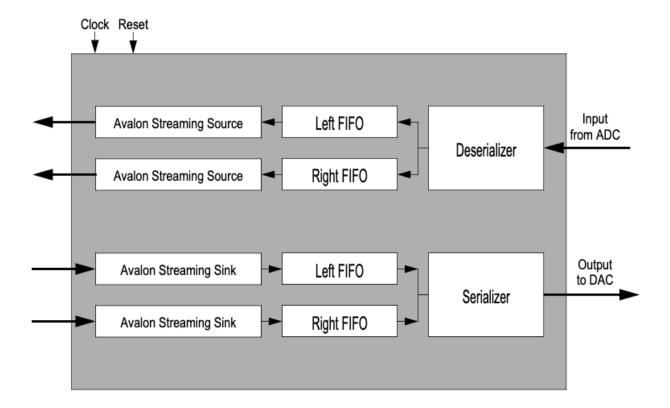

#### Audio Interface

Pitch Perfect is intended to work using the Line In and Line Out ports on the Cyclone V DE1-SOC board. To configure the board to allow us to interface with these ports in a way that made sense for our project, we set up the following components:

#### 1. Audio Clock for DE-series Boards

Configured to a frequency of 12.288 MHz to work with a 48kHz sampling rate of both the ADC and DAC according to the following specification from page 39 of the Wolfson WM8731/WM8731L CODEC manual to achieve a Base Oversampling Rate of 0. Output clk\_out serves as the clock input for the audio core and sampler components, described below.

| SAMPLING<br>RATE |          | MCLK<br>FREQUENCY |           | DIGITAL<br>FILTER |     |     |     |   |  |

|------------------|----------|-------------------|-----------|-------------------|-----|-----|-----|---|--|

| ADC              | DAC      |                   |           | TYPE              |     |     |     |   |  |

| kHz              | kHz      | MHz               | BOSR      | SR3               | SR2 | SR1 | SR0 |   |  |

| 48               | 48       | 12.288            | 0 (256fs) | 0                 | 0   | 0   | 0   | 1 |  |

|                  |          | 18.432            | 1 (384fs) | 0                 | 0   | 0   | 0   |   |  |

| 48               | 8        | 12.288            | 0 (256fs) | 0                 | 0   | 0   | 1   | 1 |  |

|                  |          | 18.432            | 1 (384fs) | 0                 | 0   | 0   | 1   | 1 |  |

| 8                | 48       | 12.288            | 0 (256fs) | 0                 | 0   | 1   | 0   | 1 |  |

|                  |          | 18.432            | 1 (384fs) | 0                 | 0   | 1   | 0   |   |  |

| 8                | 8        | 12.288            | 0 (256fs) | 0                 | 0   | 1   | 1   | 1 |  |

|                  |          | 18.432            | 1 (384fs) | 0                 | 0   | 1   | 1   | 1 |  |

| 32               | 32       | 12.288            | 0 (256fs) | 0                 | 1   | 1   | 0   | 1 |  |

|                  |          | 18.432            | 1 (384fs) | 0                 | 1   | 1   | 0   |   |  |

| 96               | 96       | 12.288            | 0 (128fs) | 0                 | 1   | 1   | 1   | 2 |  |

|                  |          | 18.432            | 1 (192fs) | 0                 | 1   | 1   | 1   |   |  |

| 44.1             | 44.1     | 11.2896           | 0 (256fs) | 1                 | 0   | 0   | 0   | 1 |  |

|                  |          | 16.9344           | 1 (384fs) | 1                 | 0   | 0   | 0   |   |  |

| 44.1             | 8        | 11.2896           | 0 (256fs) | 1                 | 0   | 0   | 1   | 1 |  |

|                  | (Note 1) | 16.9344           | 1 (384fs) | 1                 | 0   | 0   | 1   | ] |  |

| 8                | 44.1     | 11.2896           | 0 (256fs) | 1                 | 0   | 1   | 0   | 1 |  |

| (Note 1)         |          | 16.9344           | 1 (384fs) | 1                 | 0   | 1   | 0   |   |  |

| 8                | 8        | 11.2896           | 0 (256fs) | 1                 | 0   | 1   | 1   | 1 |  |

| (Note 1)         | (Note 1) | 16.9344           | 1 (384fs) | 1                 | 0   | 1   | 1   |   |  |

| 88.2             | 88.2     | 11.2896           | 0 (128fs) | 1                 | 1   | 1   | 1   | 2 |  |

|                  |          | 16.9344           | 1 (192fs) | 1                 | 1   | 1   | 1   |   |  |

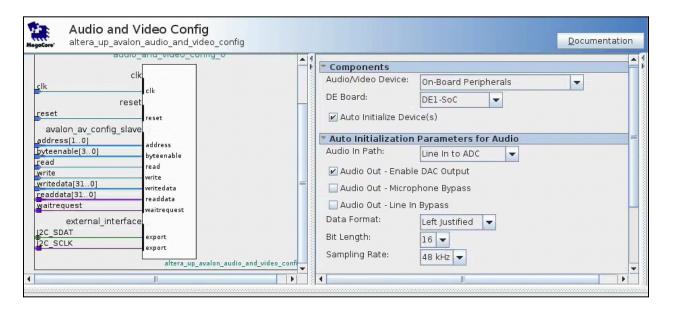

#### 2. Audio and Video Config Core

Provides a way to initialize and reconfigure the Wolfson Audio CODEC. It communicates with the CODEC through the 2-wire I2C serial bus via its <code>I2C\_SDAT</code> and <code>I2C\_SCLK</code> external interface, which connect to the board's <code>FPGA\_I2C\_SDAT</code> and <code>FPGA\_I2C\_SCLK</code> wires, respectively. It has been configured to auto-initialize the CODEC to use the Line In to ADC audio input path, the DAC to Line Out audio output path, using 16-bit left-justified samples at a sampling rate of 48kHz. Its Avalon Slave config interface is connected to the <code>software\_interface</code> component, but unused, as we don't want to allow the core to be reconfigured after its initial configuration.

#### 3. Audio Core

Provides an interface for audio input/output to the FPGA's Audio CODEC. Configured in "streaming mode" to allow us to stream values from other hardware components, and otherwise auto-initialized by the Audio and Video Config Core.

# software interface

Communicates with software via the Avalon Bus, connected to the processor's  $h2f_lw_axi_master$  output, to receive an 8-bit fixed-point "shift amount" with 6 fractional bits, then indicates to scaler how much to scale the pitch by.

```

// Input from the Avalon Bus

input logic [7:0] writedata,

input logic write,

input chipselect,

input logic [2:0] address,

// Tell the rest of the system how much to shift by (controlled by software)

output logic [7:0] shift_amt = 0,

// Fill the AV Config component's avalon slave module to quiet warnings

output logic [1:0] av_config_slave_address = 0,

output logic [3:0] av_config_slave_byteenable = 0,

output logic av_config_slave_read = 0,

output logic [31:0] av_config_slave_write = 0,

output logic [31:0] av_config_slave_writedata = 0,

input logic [31:0] av_config_slave_readdata,

```

#### sampler

Avalon streaming component to read samples of left from\_adc channel of the Wolfson Audio CODEC to a ring buffer. Connects to the avalon\_left\_channel\_source and avalon\_right\_channel\_source of the Audio Core according to the Avalon Streaming Sink specification, flashing the in\_ready inputs for one clock cycle and expecting the in\_valid and in\_data values to be set accordingly on the next cycle. Every 1024 samples read, a window is ready to be processed by the rest of the pitch scaling algorithm, so the go\_out wire is flashed high for one cycle to indicate to first\_hannifier that it should begin processing samples from the ring\_buf, as will happen for each of the following components. The 3-bit window\_start output indicates to hann\_buf whether the current window starts at index 0, 1024, 2048, 3072, or 4096 of ring\_buf. The ring buffer, ring\_buf, is a 2-port RAM component of M10K memory holding 4096 + 1024 = 5120 16-bit samples, with 2 clocks, one for a write-only input from sampler at the audio clock speed, and one for a read-only output to first\_hannifier at the main FPGA clock speed of 50MHz.

```

// Read from avalon_left_channel_source from audio codec

input logic [15:0] left_in_data,

input logic left_in_valid,

output logic left_in_ready = 0,

// Read from avalon_right_channel_source from audio codec

input logic [15:0] right_in_data,

input logic right_in_valid,

output logic right_in_ready = 0,

// Write to ring buffer

output logic [15:0] ring_buf_data,

output logic [12:0] ring_buf_addr = 0,

output logic ring_buf_wren = 0,

// Communicate with first_hannifier

output logic [2:0] window_start,

output logic [2:0] window_start,

output logic go_out = 0

```

#### first hannifier

Applies the Hann Windowing function to a window of samples from ring\_buf. All 4096 Hann Window scaling values have been stored in ROM as 16-bit fixed-point values with all 16 bits fractional. Hann Windowed values are written to pre\_fft buf, a 2-port single-clock RAM

component of M10K memory holding 4096 16-bit fixed-point words with 8 fractional bits, as are all following RAM blocks throughout the implementation.

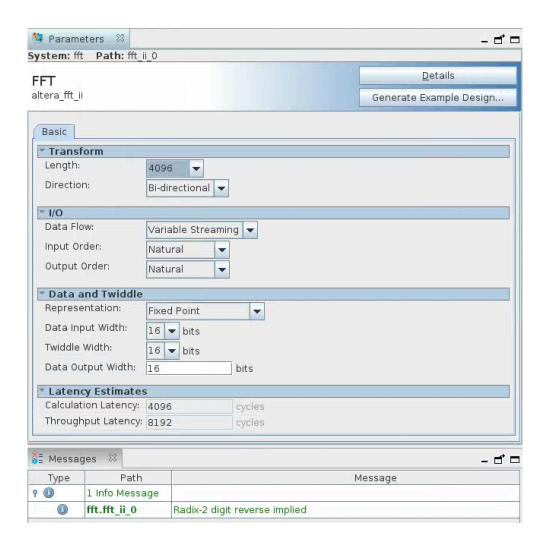

#### FFT-er

At the core of our implementation are two Fourier Transform hardware blocks. For these, we've decided to use Intel's FFT Engine rather than attempting to implement our own Fast Fourier Transform module, as we have faith that the good people at Intel were able to implement an efficient FFT module. Both our FFT and IFFT IPs were created with the following parameters:

Window length = 4096 samples (~ 92 ms) Hop length = 1024 samples (~ 23 ms)

The window length was selected to be 4096 based on the convention of using this window length in audio processing. The hop length was calculated to be 1024 based on testing the C-version of our implementation.

To initially test the FFT module, we created the IP as outlined above and generated an example file which we then analyzed using QuestaSim.

After doing so, we focused on creating a more developed wrapper module to further test and understand the functionalities of the FFT IP. This consisted of the following three files, and was developed with help from this video, with modifications made to the specifications of our project:

fft wrapper.v

This module serves as a wrapper around the FFT core. It handles input/output signals, controls, and instantiates the FFT module. It also manages signal synchronization and data flow between the FFT core and external components.

# control\_for\_fft.v

This module generates control signals required for the FFT computation. It manages signals such as validity, start of packet (SOP), end of packet (EOP), and error indications. It also handles configuration options like inverse FFT and FFT point size.

#### testbench.v

This testbench is used for verifying the functionality of the FFT wrapper and control modules. It generates clock signals, drives input signals to the FFT wrapper, and monitors the output signals. It instantiates the FFT wrapper and the NCO IP to provide input to validate its behavior under different conditions.

Although these files were successfully compiled in Quartus, we faced FFT core errors when attempting to simulate them in QuestaSim. Therefore, we moved on to creating a wrapper that is focused on interfacing the FFT IP within the necessary functionalities of the phase vocoder.

# cart\_to\_polar

Converts imaginary values to polar coordinates. Converted values are written to pre\_scaler\_mag\_buf\_0 and pre\_scaler\_phase\_buf\_0 or pre\_scaler\_mag\_buf\_1 and pre\_scaler\_phase\_buf\_1, alternating each cycle. When a window is completed, cur\_buf indicates to scaler whether the current set of values were written to buffers 0 or 1. This module utilizes an open source CORDIC module. CORDIC works as an approximation for trigonometric functions by iteratively rotating the input point by a predetermined amount that provides a convenient update rule at each step, only requiring addition and bit shifting. The update rule is as follows:

$$X_{(k+1)} = X_{k-Y} << k$$

$Y_{(k+1)} = X_{k+Y} << k$

Once the point is shifted to a 0 degree angle, it is clear what the angle and magnitude of the original point is. As the value you left on  $x_k = magnitude * scale_factor and angle = sum(r_i) from 0 to k, where r i represents the rotation factor.$

```

input logic [15:0] imag_buf_data,

output logic [12:0] imag buf addr = 0,

output logic [15:0] mag buf 0 data = 0,

output logic [11:0] mag_buf_0_addr = 0,

output logic mag buf 0 wren = 0,

phase buf 0 wren = 0,

output logic [15:0] mag buf 1 data = 0,

output logic [11:0] mag buf 1 addr = 0,

output logic mag buf 1 wren = 0,

output logic phase buf 1 wren = 0,

```

#### scaler

Performs the pitch scaling on polar values of FFT bins according to the algorithm described earlier. Reads <code>scale\_amt</code> from <code>software\_interface</code> to know how much to scale by. Requires both write and read access to output <code>post\_scaler</code> buffers to read values from previous cycles for comparison (see algorithm description section above). Also utilizes its own <code>synth\_mags</code> and <code>synth\_devs</code> buffers to hold intermediate values from the computations for output frequency bins. When a window is completed, <code>cur\_buf</code> indicates to <code>polar\_to\_cart</code> whether the current set of values were written to buffers 0 or 1.

```

output logic [11:0] mag_in_buf_0_addr = 0,

output logic [11:0] phase_in_buf_0_addr = 0,

output logic [11:0] mag_in_buf_1_addr = 0,

output logic mag out buf 0 wren = 0,

output logic [15:0] phase_out_buf_0_wrdata = 0,

input logic [15:0] mag_out_buf_1_rdata,

output logic [15:0] mag out buf 1 wrdata = 0,

output logic [11:0] mag_out_buf_1_wraddr = 0,

```

```

mag_out_buf_1_wren = 0,

output logic [15:0] phase_out_buf_1_wrdata = 0,

input logic [15:0] synth_mags_rdata,

output logic [11:0] synth_mags_wraddr = 0,

output logic synth mags wren = 0,

output logic synth devs wren = 0,

```

#### polar to cart

Converts polar coordinates back to imaginary values. Utilizes a CORDIC approach to computing sine and cosine values. Converted values are written to pre\_ifft real buf and pre\_ifft imag buf.

```

// Read from scaler_mag_buf_1

input logic [15:0] mag_buf_1_data,

output logic [11:0] mag_buf_1_addr = 0,

// Read from scaler_phase_buf_1

input logic [15:0] phase_buf_1_data,

output logic [11:0] phase_buf_1_addr = 0,

// Write to pre_ifft_real_buf

output logic [15:0] real_buf_data,

output logic [12:0] real_buf_addr = 0,

output logic real_buf_wren = 0,

// Write to pre_ifft_imag_buf

output logic [15:0] imag_buf_data,

output logic [12:0] imag_buf_addr = 0,

output logic [12:0] imag_buf_wren = 0,

// Communicate with iffter

output logic go_out = 0

```

#### IFFT-er

The inverse FFT follows the same wrapper module as the FFT, however, the input of "inverse" is set to 1, as seen below:

#### stitcher

Applies the Hann Windowing function to a window of samples from post\_ifft\_buf. Values are either overwritten or added to those in stitched\_buf. The 2-bit window\_start output indicates to emitter whether the current window starts at index 0, 1024, 2048, or 3072.

```

// Communicate with iffter

input logic go_in,

// Read from post_ifft_buf

input logic [15:0] in_buf_data,

output logic [11:0] in_buf_addr = 0,

// Read from Hann Window ROM

input logic [15:0] hann_rom_data,

output logic [11:0] hann_rom_addr = 0,

```

```

// Write to stitched_buf

output logic [15:0] out_buf_data = 0,

output logic [11:0] out_buf_addr = 0,

output logic out_buf_wren = 0,

// Communicate with emitter

output logic [1:0] window_start,

output logic go_out = 0

```

#### emitter

Avalon streaming component to write samples to both left and right to\_dac channels of the Wolfson Audio CODEC. Connects to the avalon\_left\_channel\_sink and avalon\_right\_channel\_sink of the Audio Core according to the Avalon Streaming Sink specification, flashing the out\_valid for one clock cycle with the next sample of data on out\_data after seeing out\_ready flashed. Per the Audio Core specification, both avalon\_left\_channel\_sink and avalon\_left\_channel\_sink need to be written to for the Audio CODEC to not block and the sample to be played.

```

// Communicate with stitcher

input logic [1:0] window_start,

input logic go_in,

// Write to avalon_left_channel_sink of audio codec

output logic [15:0] left_out_data = 0,

output logic left_out_valid = 0,

input logic left_out_ready,

// Write to avalon_right_channel_sink of audio codec

output logic [15:0] right_out_data = 0,

output logic right_out_valid = 0,

input logic right_out_valid = 0,

input logic right_out_ready

```

# Resource Budgets: Memory Requirement Estimation

From the table entry above, we see that our chosen FFT engine uses 14 of our 397 available M10K memory blocks.

In our implementation, as seen in the system block diagram utilizes 14 intermediary buffers of length 4096. Each sample is 16 bits.

Additionally, we utilizes two ring buffers which contain 5120 16-bit samples

Finally, we utilize one 4096 16-bit ROM.

The memory consumption of our buffers is thus 112 M10K Blocks.

The FFT Blocks utilize the following amounts of memory based on our specifications.

| Cyclone V | Variable<br>Streaming<br>Floating<br>Point | 4,096 | _ | 13,945 | 60 | 138 |  | 22,615 | 701 | 132 |  |

|-----------|--------------------------------------------|-------|---|--------|----|-----|--|--------|-----|-----|--|

|-----------|--------------------------------------------|-------|---|--------|----|-----|--|--------|-----|-----|--|

Because we utilize two FFT Blocks, one for the forward and reverse processes we utilize a total of 279 M10K Blocks.

Together with the buffers and ROMs the total memory consumption of this project is 391 M10K Blocks.

#### **Who Did What**

#### Maria

- Researched pitch shifting algorithms

- Researched various implementations of the fast fourier transform for pitch shifting

- Implemented the Cooley-Tukey FFT algorithm in C

- Tested with a variety of inputs, including applying FFT and IFFT on a 4096 size window to ensure that the final output was equivalent to the input

- Helped with debugging the C vocoder algorithm

- Created converters in python for testing purposes

- Researched the FFT intel core module

- o Identified the best options of the module to use within our phase vocoder

- Tested a generated example using QuestaSim

- Created a FFT wrapper and testbench for testing purposes

- Compiled the files successfully in Quartus

- Ran into errors with protected files while compiling in Questasim

- Implemented fft and ifft hardware components

#### Sanjay

- Researched pitch shifting algorithms

- Wrote C algorithm to simulate input buffer, Hann window scaling, and audio outputting

- Wrote bash script to integrate Python wav convertors and C simulation

- Debugged and contributed to C vocoder algorithm to remove noise

- Converted C vocoder algorithm to operate on polar coordinates instead from cartesian

- Attempted to set up ROM components for Hann Window coefficients and CORDIC polar conversion

- Researched and implemented fixed point calculations, computing necessary coefficients and writing code for computing moduli

- Developed polar conversion hardware components

- Contributed to scaler hardware component

#### Steven

- Researched various pitch scaling algorithms

- Implemented two different pitch scaling algorithms in Python

- Implemented C vocoder algorithm

- Created real-time C implementation wrapper

- Created file type converters in Python

- Attempted to configure and connect to DE1-SOC Audio module

- Configured top level hardware system in Platform Designer

- Designed interfaces of all hardware components

- Created skeletons of all hardware components with necessary I/O to connect in Platform Designer

- Implemented sampler, first\_hannifier, and emitter hardware components, and contributed to scaler

#### **Lessons Learned**

#### How to Perform Fixed Point Computation

In this project, we learned about fixed point representation, something none of us had heard of before. We utilized fixed point representation throughout our project such as in our FFT implementation as well as our polar/cartesian convertors.

# Hardware Function Approximations and "Cutting Corners"

In this project, we learned about fixed point representation, something none of us had heard of before. We utilized fixed point representation throughout our project such as in our FFT implementation as well as our polar/cartesian convertors. One of the biggest lessons of this project was learning how difficult it is to compute certain functions that we often take for granted in hardware. Hey to our algorithm were functions such as fmodf, atan2, and sine and cosine. We learned about approximation methods for computing trigonometric functions. We utilized the CORDIC algorithm for this. Additionally, we were able to factor out fmodf by carefully inspecting the data that ran through our algorithm. We noticed that the values were bounded. Thus, we could

avoid utilizing a costly fixed point mod algorithm, achieving the same effect through addition and division.

#### **General Lessons**

- Simulate even the most simple algorithms with low-level C software to confirm that they work before building them in hardware

- Make your software simulation match the hardware as closely as possible it is easier to think about things in terms of software first

- Give yourself more time to implement hardware

- It takes a serious amount of time to figure out how to interface with the board

#### How to open up Questasim

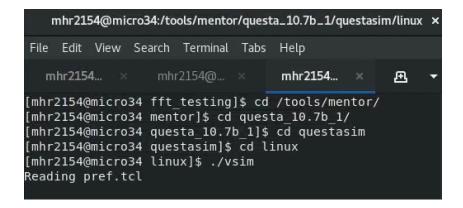

Although a very trivial part of a much more complicated project, we ran into errors with a broken pathway for "vsim" and had to dig into many different folders to find the correct pathway and open up Questasim for testing. Additionally, we learned that you can directly link Questasim to Quartus through settings, so that when you run "RTL simulation" it opens up and simulates the top-level module in Questasim.

#### How to work on hardware components

We found there to be a steep learning curve in learning the various steps needed for working on the hardware implementation of our project. Many specific commands need to be run in a specific order for things to work properly, and we didn't love scrolling through the entire Lab 3 document each time to remember them. To that end, we created the following guide for ourselves to follow to simplify the process, which we are providing here in the hopes that it will be useful for some future group. To those groups however, please note that we did not actually get our project working on the

FPGA as we intended, so this could be completely wrong, and you may want to check with Professor Edwards or a TA before following our instructions.

- To create a new component

- To define the component's inputs/outputs, copy the sv file for any other component (basic\_component.sv) and edit the copy to have the inputs/outputs desired

- To figure out what inputs/outputs are needed, look at what it connects to

- If it connects to a standard library component, right click that component and click edit, then check "show signals" to see which wires each interface (ex. Avalon Memory Mapped Slave) uses. You will set the interfaces in the next step

- To add the new component to our system, do

- qsys-edit soc\_system.qsys

- File > New Component

- Give it a name and display name

- Files > Synthesis Files > Add File > new\_component.sv

- Click Analyze Synthesis Files to have qsys create a component from the System Verilog file

- o Probably will need to fix errors in the .sv file

- Set Top-Level Module to this file

- Signals & Interfaces tab

- Create interfaces (ex. Avalon Memory Mapped Slave) as needed to set the input/output logic to match those

- Click Finish to create a \_hw.tcl file for the new component

- ONLY if it is a software interfacing component (will also have to edit kernel module so really just stick with one of these) in a separate terminal tab, edit component\_name\_hw.tcl to add the following under the module component\_name section

- set module assignment embeddedsw.dts.vendor "csee4840"

- set\_module\_assignment embeddedsw.dts.name "full\_name"

- o set module assignment embeddedsw.dts.group "name"

- In IP Catalog > Project (to the left), click the new component, then click [+Add...] to add it to our system

- To use pre-made Altera components, you cannot just add them in Platform Designer. You must create files for them using Quartus.

- Right click the various parts of a component to connect them to other parts of other components

- Edit the logic inside a component by editing it's .sv file

- To test on the board

- Click Generate HDL in the Platform Designer to generate the Verilog for the project

- Run make quartus to generate output\_files/soc\_system.sof

- Run make rbf to generate output files/soc system.rbf

- Run embedded\_command\_shell.sh

- Run make dtb to generate soc system.dtb

- Plug the board in to power, ethernet, and micro-USB (black cable to the PC)

- Run screen /dev/ttyUSB0 115200

- Power on the board

- From the screened board terminal

- Login with root, CSee4840!

- Run *ifup eth0* to connect to the internet

- Run mount /dev/mmcblk0p1 /mnt

- Run scp <uni>@micro<XX>.ee.columbia.edu:~/pitch-perfect/hardware/hw/output\_fil es/soc\_system.rbf /mnt

- scp

<uni>@micro<XX>.ee.columbia.edu:~/pitch-perfect/hardware/hw/soc\_syste

m.dtb/mnt ← not in output files!

- Run sync

- Run reboot

# **Complete File Listing**

#### **Software Simulation Files**

software-simulation/python-vocoder/vocoder.py

```

vocoder.py

Pitch scaling algorithm following

https://github.com/BelaPlatform/bela-online-course/blob/master/lectures/le

cture-20/code-examples/fft-pitchshift.zip

using Python based on

https://github.com/JentGent/pitch-shift/blob/main/audios.ipynb

"""

import librosa

import numpy as np

import soundfile as sf

```

```

import sys

WINDOW SIZE = 4096 # win len, n fft

HOP LEN = 1024 # hop len

PHASE SHIFT AMOUNT = 2 ** (5 / 12) \# scaling

waveform, samp rate = librosa.load(sys.argv[1], sr=None, mono=True) #

waveform, sr # used to not be mono

num samples = waveform.shape[0] # og len

stft result = librosa.stft(waveform, n fft=WINDOW SIZE,

hop length=HOP LEN, win length=WINDOW SIZE) # anls stft

n fft bins, n fft frames = stft result.shape # n anls freqs,

n anls frames, used to also have "channels" count

stft result = np.transpose(stft result)

stft result scaled = []

prev anal phases = np.zeros(n fft bins)

prev synth phases = np.zeros(n fft bins)

for idx, frame in enumerate(stft result):

if idx == 0:

mags = np.abs(frame)

phases = np.angle(frame)

dphases from prev = phases - prev anal phases

bin_center_freqs = np.arange(n fft bins) * 2 * np.pi / WINDOW SIZE #

how much each bin should move per sample

dphases from expected = dphases from prev - (bin center freqs *

HOP LEN)

```

```

dphases from expected = np.mod(dphases from expected + (3 * np.pi), 2

np.pi) - np.pi # wrap to [-pi, pi]

bin deviations = (dphases from expected * WINDOW SIZE) / (2 * np.pi *

HOP LEN) # how many bins we should change (over a whole bin length)

new bins = (np.arange(n fft bins) + bin deviations) *

PHASE SHIFT AMOUNT

new bin nums = np.rint(new bins)

synth mags = np.zeros(n fft bins)

synth deviations = np.zeros(n fft bins)

synth mags[int(new bin num)] += mags[old idx]

synth deviations[int(new bin num)] += new bins[old idx] -

new bin nums[old idx]

phase remainders = ((synth deviations) * 2 * np.pi * HOP LEN) /

WINDOW SIZE

synth phases = prev synth phases + phase remainders + (2 * np.pi *

bin center freqs * HOP LEN)

synth phases = np.mod(synth phases + (3 * np.pi), 2 * np.pi) - np.pi #

wrap to [-pi, pi]

stft_result_scaled.append(synth_mags * np.exp(synth_phases * 1j))

prev anal phases = phases

prev synth phases = synth phases

stft result scaled = np.array(stft result scaled)

stft result scaled = np.transpose(stft result scaled)

new waveform = librosa.istft(stft result scaled, n fft=WINDOW SIZE,

hop length=HOP LEN, win length=WINDOW SIZE)

sf.write(sys.argv[2], new waveform, samp rate, 'PCM 24')

```

# software-simulation/realtime/main.c

```

#include <stdlib.h>

#include <stdio.h>

#include <stdlib.h>

#include <math.h>

#include <errno.h>

#include "../fft/fft.h"

#include "../scaling/scaling.h"

#define WINDOW SIZE 4096

#define HOP LENGTH 1024

\#define PHASE SHIFT AMOUNT(x) pow(2.0, (x / 12.0))

void hannify(float* inputSamples, int startIdx, float* output) {

output[i] = inputSamples[(i + startIdx) % (WINDOW SIZE +

HOP LENGTH)] * w;

float inputSamples[WINDOW SIZE + HOP LENGTH];

int inputWindowStart = 0;

int inputCurIdx = 0;

float hanned1[WINDOW SIZE];

float hanned2[WINDOW SIZE];

float *fftRealBufs[2];

float *fftImagBufs[2];

float *shiftRealBufs[2];

float *shiftImagBufs[2];

int fftBufIdx = 0;

float fftReal1[WINDOW SIZE];

```

```

float fftImag1[WINDOW SIZE];

float fftReal2[WINDOW SIZE];

float fftImag2[WINDOW SIZE];

float shiftReal1[WINDOW SIZE];

float shiftImag1[WINDOW SIZE];

float shiftReal2[WINDOW SIZE];

float shiftImag2[WINDOW SIZE];

float ifftReal[WINDOW SIZE];

float ifftImag[WINDOW SIZE];

float stitcher[WINDOW SIZE];

int stitcherPtr = 0;

char *curLine;

size t curLineLen = 0;

int main(int argc, char** argv)

if (argc != 2) {

fprintf(stderr, "Usage: %s <semitone-shift> \n", argv[0]);

int semitoneShift = strtol(argv[1], NULL, 10);

fftRealBufs[0] = fftReal1;

fftImagBufs[0] = fftImag1;

fftRealBufs[1] = fftReal2;

fftImagBufs[1] = fftImag2;

shiftRealBufs[0] = shiftReal1;

shiftImagBufs[0] = shiftImag1;

shiftRealBufs[1] = shiftReal2;

shiftImagBufs[1] = shiftImag2;

fftReal1[i] = 0;

fftImag1[i] = 0;

```

```

fftReal2[i] = 0;

fftImag2[i] = 0;

shiftReal1[i] = 1;

shiftImag1[i] = 1;

shiftReal2[i] = 1;

shiftImag2[i] = 1;

ifftReal[i] = 0;

ifftImag[i] = 0;

stitcher[i] = 0;

while (-1 != getline(&curLine, &curLineLen, stdin)) {

inputSamples[inputCurIdx] = strtof(curLine, NULL) * 0.8; // to

if (inputCurIdx == (inputWindowStart + WINDOW SIZE) %

hannify(inputSamples, inputWindowStart, hanned1);

fftRealBufs[fftBufIdx][i] = hanned1[i];

fftImagBufs[fftBufIdx][i] = 0;

rearrange(fftRealBufs[fftBufIdx], fftImagBufs[fftBufIdx],

WINDOW SIZE);

compute(fftRealBufs[fftBufIdx], fftImagBufs[fftBufIdx],

WINDOW SIZE);

```

```

processTransformed(fftRealBufs[(fftBufIdx + 1) % 2],

fftImagBufs[(fftBufIdx + 1) % 2],

fftRealBufs[fftBufIdx],

fftImagBufs[fftBufIdx],

shiftRealBufs[(fftBufIdx + 1) % 2],

shiftImagBufs[(fftBufIdx + 1) % 2],

shiftRealBufs[fftBufIdx],

shiftImagBufs[fftBufIdx],

PHASE SHIFT AMOUNT (semitoneShift));

ifftReal[i] = shiftRealBufs[fftBufIdx][i];

ifftImag[i] = shiftImagBufs[fftBufIdx][i];

inverseCompute(ifftReal, ifftImag, WINDOW SIZE);

hannify(ifftReal, 0, hanned2);

stitcher[(stitcherPtr + i) % WINDOW SIZE] +=

(hanned2[i] / 2.0);

(hanned2[i] / 2.0);

printf("%f\n", stitcher[stitcherPtr + i]);

```

#### software-simulation/fft/fft.c

```

#include <math.h>

#include <stdio.h>

#include "fft.h"

void rearrange(float real[], float imaginary[], const unsigned int N)

{

unsigned int target = 0;

for (unsigned int position = 0; position < N; position++)

{

if (target > position)

(

const float temp_real = real[target];

const float temp_imaginary = imaginary[target];

real[target] = real[position];

imaginary[target] = imaginary[position];

real[position] = temp_real;

imaginary[position] = temp_imaginary;

}

unsigned int mask = N;

while (target & (mask >>= 1))

target &= ~mask;

}

}

```

```

target |= mask;

void compute(float real[], float imaginary[], const unsigned int N)

const float pi = -3.14159265358979323846;

for (unsigned int step = 1; step < N; step <<= 1)</pre>

const unsigned int jump = step << 1;</pre>

const float step d = (float)step;

float twiddle imaginary = 0.0;

for (unsigned int group = 0; group < step; group++)</pre>

for (unsigned int pair = group; pair < N; pair += jump)</pre>

const unsigned int match = pair + step;

const float product real = twiddle real * real[match] -

twiddle imaginary * imaginary[match];

const float product imaginary = twiddle imaginary *

real[match] + twiddle real * imaginary[match];

real[match] = real[pair] - product real;

imaginary[match] = imaginary[pair] - product imaginary;

real[pair] += product real;

imaginary[pair] += product imaginary;

if (group + 1 == step)

```

```

float angle = pi * ((float)group + 1) / step d;

twiddle real = cos(angle);

twiddle imaginary = sin(angle);

void inverseCompute(float real[], float imaginary[], const unsigned int N)

imaginary[i] = -imaginary[i];

rearrange(real, imaginary, N);

compute(real, imaginary, N);

imaginary[i] = -imaginary[i];

real[i] *= scale;

imaginary[i] *= scale;

```

# software-simulation/fft/fft.h

```

#ifndef FFT_H

#define FFT_H

#include <stddef.h> // for size_t

struct complex_num {

float real;

float imsag;

};

void rearrange(float real[], float imaginary[], const unsigned int N);

void compute(float real[], float imaginary[], const unsigned int N);

void inverseCompute(float real[], float imaginary[], const unsigned int N);

#endif

```

#### software-simulation/fft/main.c

```

inverseCompute(input real1, input imaginary1, N1);

printf("\nIFFT Output:\n");

for (unsigned int i = 0; i < N1; ++i) {

printf("%f + %fi\n", input real1[i], input imaginary1[i]);

float input real2[] = \{1.0, 2.0, 3.0, 4.0\};

float input imaginary2[] = {0.0, 0.0, 0.0, 0.0};

rearrange(input real2, input imaginary2, N2);

compute(input real2, input imaginary2, N2);

printf("\nFFT Output:\n");

printf("%f + %fi\n", input real2[i], input imaginary2[i]);

inverseCompute(input real2, input imaginary2, N2);

printf("\nIFFT Output:\n");

for (unsigned int i = 0; i < N2; ++i) {

printf("%f + %fi\n", input real2[i], input imaginary2[i]);

const unsigned int N3 = 8;

float input real3[] = \{1.0, 2.0, 3.0, 4.0, 5.0, 6.0, 7.0, 8.0\};

float input imaginary3[] = {0.0, 0.0, 0.0, 0.0, 0.0, 0.0, 0.0};

rearrange(input real3, input imaginary3, N3);

compute(input real3, input imaginary3, N3);

printf("\nFFT Output:\n");

for (unsigned int i = 0; i < N3; ++i) {

printf("%f + %fi\n", input real3[i], input imaginary3[i]);

```

```

inverseCompute(input real3, input imaginary3, N3);

printf("\nIFFT Output:\n");

for (unsigned int i = 0; i < N3; ++i) {

printf("%f + %fi\n", input real3[i], input imaginary3[i]);

const unsigned int N4 = 8;

float input real4[] = {0.34785901, 0.71862502, 0.11248643, 0.59830784,

0.90372152, 0.44128975, 0.29513480, 0.87653024};

rearrange(input real4, input imaginary4, N4);

compute(input real4, input imaginary4, N4);

printf("FFT Output:\n");

for (unsigned int i = 0; i < N4; ++i) {

printf("%f + %fi\n", input real4[i], input imaginary4[i]);

inverseCompute(input real4, input imaginary4, N4);

printf("\nIFFT Output:\n");

for (unsigned int i = 0; i < N4; ++i) {

printf("%f + %fi\n", input real4[i], input imaginary4[i]);

const unsigned int N5 = 4096;

float input real5[N5];

float input imaginary5[N5] = {0}; // Initialize with zeros

FILE *file = fopen("nums.txt", "r");

if (file != NULL) {

fscanf(file, "%f", &input_real5[i]);

```

```

fclose(file);

printf("length of real: %lu",

sizeof(input real5)/sizeof(input real5[0]));

rearrange(input real5, input imaginary5, N5);

compute(input real5, input imaginary5, N5);

FILE *fft file = fopen("fft.txt", "w");

if (fft file != NULL) {

fprintf(fft file, "%f + %fi\n", input real5[i],

input imaginary5[i]);

fclose(fft file);

printf("Error opening fft.txt for writing.\n");

inverseCompute(input real5, input imaginary5, N5);

FILE *ifft file = fopen("ifft.txt", "w");

if (ifft file != NULL) {

fprintf(ifft file, "%f + %fi\n", input real5[i],

input_imaginary5[i]);

printf("Error opening ifft.txt for writing.\n");

```

```

} else {

printf("Error opening nums.txt for reading.\n");

}

return 0;

}

```

## software-simulation/scaling/scaling.c

```

#include <stdio.h>

#include <math.h>

#include "scaling.h"

#define WINDOW SIZE 4096

#define HOP LENGTH 1024

float synthMags[WINDOW SIZE / 2];

float synthBinDeviations[WINDOW SIZE / 2];

double phaseDifference(float real1, float imag1, float real2, float imag2)

return atan2(imag2, real2) - atan2(imag1, real1);

float wrapPhase(float phaseIn)

if (phaseIn >= 0)

return fmodf(phaseIn + M PI, 2.0 * M PI) - M PI;

return fmodf(phaseIn - M_PI, -2.0 * M_PI) + M_PI;

void processTransformed(float* realPrev, float* imagPrev, float* realNew,

float* imagNew, float* realOutPrev, float*

imagOutPrev,

```

```

float* realOutNew, float* imagOutNew, double

phaseScaleAmount) {

synthMags[i] = 0;

synthBinDeviations[i] = 0;

float dPhase;

if (realNew[i] == 0 && imagNew[i] == 0) {

else if (realPrev[i] == 0 && imagPrev[i] == 0) {

dPhase = i * 2 * M PI * HOP LENGTH / WINDOW SIZE;

dPhase = phaseDifference(realPrev[i], imagPrev[i], realNew[i],

imagNew[i]);

float expectedDPhase = i * 2 * M PI * HOP LENGTH / WINDOW SIZE;

float dPhaseFromExpected = dPhase - expectedDPhase; // compute

float binDeviation = wrapPhase(dPhaseFromExpected) * WINDOW SIZE /

(2 * M PI * HOP LENGTH);

float newBin = (i + binDeviation) * phaseScaleAmount;

int newBinNum = fmax(fmin(round(newBin), WINDOW SIZE - 1), 0); //

float newBinDeviation = newBin - newBinNum;

synthMags[newBinNum] += sgrt((realNew[i] * realNew[i]) +

(imagNew[i] * imagNew[i]));

synthBinDeviations[newBinNum] += newBinDeviation;

```

```

float newPhase;

if (synthMags[i] == 0) {

newPhase = 0;

else if (realOutPrev[i] == 0 && imagOutPrev[i] == 0) {

newPhase = synthBinDeviations[i];

float phaseRemainder = synthBinDeviations[i] * 2 * M PI *

HOP LENGTH / WINDOW SIZE;

newPhase = atan2(imagOutPrev[i], realOutPrev[i]) +

phaseRemainder + (i * 2 * M PI * HOP LENGTH / WINDOW SIZE);

realOutNew[i] = cos(newPhase) * synthMags[i];

imagOutNew[i] = sin(newPhase) * synthMags[i];

if (i != 0) {

realOutNew[WINDOW SIZE - i] = cos(-newPhase) * synthMags[i];

imagOutNew[WINDOW SIZE - i] = sin(-newPhase) * synthMags[i];

void simpleTransform(float* realPrev, float* imagPrev, float* realNew,

float* imagNew, float* realOutPrev, float*

imagOutPrev,

float* realOutNew, float* imagOutNew, double

phaseScaleAmount) {

synthMags[i] = 0;

if (realNew[i] == 0 && imagNew[i] == 0) {

```

```

int newBinNum = round(i * phaseScaleAmount);

synthMags[newBinNum] += sqrt((realNew[i] * realNew[i]) +

(imagNew[i] * imagNew[i]));

float newPhase;

if (synthMags[i] == 0) {

newPhase = 0;

else if (realOutPrev[i] == 0 && imagOutPrev[i] == 0) {

newPhase = 0;

newPhase = atan2(imagOutPrev[i], realOutPrev[i]) + (i * 2 *

M PI * HOP LENGTH / WINDOW SIZE);

realOutNew[i] = cos(newPhase) * synthMags[i];

imagOutNew[i] = sin(newPhase) * synthMags[i];

if (i != 0) {

realOutNew[WINDOW SIZE - i] = cos(-newPhase) * synthMags[i];

imagOutNew[WINDOW SIZE - i] = sin(-newPhase) * synthMags[i];

```

## software-simulation/scaling/scaling.h

```

#ifndef SCALING_H

#define SCALING_H

double phaseDifference(float real1, float imag1, float real2, float

imag2);

void processTransformed(float* realPrev, float* imagPrev, float* realNew,

```

## software-simulation/scaling/main.c

```

#include <stdio.h>

#include <math.h>

#include "scaling.h"

#define WINDOW SIZE 4096

int approx(float a, float b) {

if (!(fabs(a - b) < 0.001)) {

return fabs(a - b) < 0.001;

int main(int argc, char** argv) {

float testReal1[WINDOW SIZE]; // previous FFT transform

float testImag1[WINDOW SIZE];

float testReal2[WINDOW SIZE]; // current FFT transform

float testImag2[WINDOW SIZE];

float testPrevReal[WINDOW SIZE]; // previous pitch scaled

float testPrevImag[WINDOW SIZE];

float testOutImag[WINDOW SIZE];

```

```

printf("Test 1: No change\n");

int passed = 1;

testReal1[i] = 1.0;

testImag1[i] = 0.0;

testReal2[i] = 1.0;

testImag2[i] = 0.0;

testPrevReal[i] = 1.0;

testPrevImag[i] = 0.0;

processTransformed(testReal1, testImag1, testReal2, testImag2,

testPrevReal, testPrevImag, testOutReal,

testOutImag,

pow(2.0, 0.0));

if (!approx(testOutReal[i], 1.0) || !approx(testOutImag[i], 0.0)) {

printf(" for i = %d\n", i);

passed = 0;

if (passed) {

printf("Passed\n");

printf("Failed\n");

printf("Test 2: Simple rotation\n");

passed = 1;

testReal1[i] = 1.0;

testImag1[i] = 0.0;

testReal2[i] = 0.0;

testImag2[i] = 1.0;

testPrevReal[i] = 0.0;

```

```

testPrevImag[i] = 1.0;

processTransformed(testReal1, testImag1, testReal2, testImag2,

testPrevReal, testPrevImag, testOutReal,

testOutImag,

pow(2.0, 0.0));

if (!approx(testOutReal[i], -1.0) || !approx(testOutImag[i], 0.0))

printf(" for i = %d\n", i);

passed = 0;

if (passed) {

printf("Passed\n");

printf("Failed\n");

printf("Test 3: Shifted start\n");

passed = 1;

testReal1[i] = 1.0;

testImag1[i] = 0.0;

testReal2[i] = 0.0;

testImag2[i] = 1.0;

testPrevReal[i] = -1.0;

testPrevImag[i] = 0.0;

processTransformed(testReal1, testImag1, testReal2, testImag2,

testPrevReal, testPrevImag, testOutReal,

testOutImag,

pow(2.0, 0.0));

```

```

if (!approx(testOutReal[i], 0.0) || !approx(testOutImag[i], -1.0))

printf(" for i = %d n", i);

passed = 0;

if (passed) {

printf("Passed\n");

printf("Failed\n");

printf("Test 4: Different Magnitudes\n");

passed = 1;

testReal1[i] = 1.0;

testImag1[i] = 0.0;

testReal2[i] = 0.0;

testImag2[i] = 2.0;

testPrevReal[i] = -1.0;

testPrevImag[i] = 0.0;

processTransformed(testReal1, testImag1, testReal2, testImag2,

testPrevReal, testPrevImag, testOutReal,

testOutImag,

pow(2.0, 0.0));

if (!approx(testOutReal[i], 0.0) || !approx(testOutImag[i], -2.0))

printf(" for i = %d\n", i);

passed = 0;

if (passed) {

```

```

printf("Passed\n");

printf("Failed\n");

printf("Test 5: Scaled shifts up\n");

passed = 1;

testReal1[i] = 1.5;

testImag1[i] = 1.5;

testReal2[i] = 0.0;

testImag2[i] = 2.0;

testPrevReal[i] = -3.5;

testPrevImag[i] = -3.5;

processTransformed(testReal1, testImag1, testReal2, testImag2,

testPrevReal, testPrevImag, testOutReal,

testOutImag,

pow(2.0, 1.0));

if (!approx(testOutReal[i], sqrt(2)) || !approx(testOutImag[i],

-sqrt(2))) {

printf(" for i = %d\n", i);

passed = 0;

if (passed) {

printf("Passed\n");

printf("Failed\n");

printf("Test 6: Scaled shifts down\n");

passed = 1;

```

```

testReal1[i] = 0.4;

testImag1[i] = 0.4;

testReal2[i] = -0.6;

testImag2[i] = -0.6;

testPrevReal[i] = -1.0;

testPrevImag[i] = 0.0;

processTransformed(testReal1, testImag1, testReal2, testImag2,

testPrevReal, testPrevImag, testOutReal,

testOutImag,

pow(2.0, -1.0));

if (!approx(testOutReal[i], 0.0) || !approx(testOutImag[i],

sqrt(0.72))) {

passed = 0;

if (passed) {

printf("Passed\n");

printf("Failed\n");

printf("Test 7: Shifting backwards\n");

passed = 1;

testReal1[i] = 0.0;

testImag1[i] = 1.0;

testReal2[i] = 1.0;

testImag2[i] = 0.0;

testPrevReal[i] = 0.0;

testPrevImag[i] = -1.0;

processTransformed(testReal1, testImag1, testReal2, testImag2,

```

```

testPrevReal, testPrevImag, testOutReal,

testOutImag,

pow(2.0, 0.0));

if (!approx(testOutReal[i], -1.0) || !approx(testOutImag[i], 0.0))

printf(" for i = %d\n", i);

passed = 0;

if (passed) {

printf("Passed\n");

printf("Failed\n");

printf("Test 8: Prev FFT 0\n");

passed = 1;

testReal1[i] = 0.0;

testImag1[i] = 0.0;

testReal2[i] = 1.2;

testImag2[i] = -3.4;

testPrevReal[i] = -5.6;

testPrevImag[i] = 7.8;

processTransformed(testReal1, testImag1, testReal2, testImag2,

testPrevReal, testPrevImag, testOutReal,

testOutImag,

pow(2.0, 1.2));

if (!approx(testOutReal[i], 1.2) || !approx(testOutImag[i], -3.4))

printf(" for i = %d\n", i);

passed = 0;

```

```

if (passed) {

printf("Passed\n");

printf("Failed\n");

printf("Test 9: Prev output 0\n");

passed = 1;

testImag1[i] = 3.4;

testReal2[i] = -5.6;

testImag2[i] = -7.8;

testPrevReal[i] = 0.0;

testPrevImag[i] = 0.0;

processTransformed(testReal1, testImag1, testReal2, testImag2,

testPrevReal, testPrevImag, testOutReal,

testOutImag,

pow(2.0, 0.0));

if (!approx(testOutReal[i], -5.6) || !approx(testOutImag[i], -7.8))

printf(" for i = %d n", i);

passed = 0;

if (passed) {

printf("Passed\n");

printf("Failed\n");

```

```

}

```

# software-simulation/converters/txter.py

```

import sys

from scipy.io import wavfile

import numpy as np

samplerate, data = wavfile.read(sys.argv[1])

# print line count

if len(sys.argv) > 2:

with open(sys.argv[2], 'w') as file:

for sample in data:

# if sample is a list, write the first element

if isinstance(sample, np.ndarray):

file.write(str(sample[0]) + '\n')

else:

file.write(str(sample) + '\n')

else:

for sample in data:

if isinstance(sample, np.ndarray):

print(sample[0])

else:

print(sample)

```

# software-simulation/converters/waver.py

```

import numpy as np

import wave

import sys

def read_samples_from_file(filename):

samples = []

if filename is not None:

with open(filename, 'r') as file:

```

```

samples = [float(sample) for sample in file.readlines()]

else:

samples = [float(sample) for sample in sys.stdin.readlines()]

return np.array(samples)

def write wav file(samples, filename, sample rate=48000, amplitude=1):

wav file = wave.open(filename, 'w')

wav file.setparams((1, 2, sample rate, len(samples), 'NONE', 'not

compressed'))

# Scale samples to fit within amplitude range

scaled_samples = np.int16(samples * amplitude)

# Convert the samples to bytes

samples_bytes = scaled samples.tobytes()

# Write the bytes to the wav file

wav file.writeframes(samples bytes)

# Close the wav file

wav file.close()

if name == " main ":

# Change this to the path of your input file

input filename = None

output filename = None

if len(sys.argv) == 2:

output filename = sys.argv[1]

elif len(sys.argv) == 3:

input filename = sys.argv[1]

output filename = sys.argv[2]

else :

# print two usage options: one for reading from stdin and one for

reading from a file

```

```

# Read samples from input file

samples = read_samples_from_file(input_filename)

# Write samples to output wav file

write_wav_file(samples, output_filename)

print("WAV file generated successfully.")

```

#### software-simulation/setup.sh

```

#!/bin/bash

# Check for the presence of the requirements.txt file

if [ ! -f "requirements.txt" ]; then

exit 1

fi

VENV NAME="venv"

activate venv() {

echo "Activating the virtual environment..."

source $VENV NAME/bin/activate

install deps() {

echo "Installing dependencies from requirements.txt..."

pip install -r requirements.txt || { echo "Installation failed"; exit

1; }

```

```

if [ -d "$VENV NAME" ]; then

activate venv

trap 'rm -f .current requirements.txt' EXIT

pip freeze > .current requirements.txt

DIFF=$(diff -u .current requirements.txt requirements.txt | grep '^\+'

if [ "$DIFF" -ne 0 ]; then

echo "Dependencies in the virtual environment do not match

install deps

echo "All dependencies are up to date."

else

python3 -m venv $VENV NAME

echo "Failed to create virtual environment."

install deps

fi

echo "To activate the virtual environment in the future, use the command:

source $VENV NAME/bin/activate"

echo "To deactivate an active virtual environment, use the command:

deactivate"

```

```

# Make realtime

echo "Building the realtime executable..."

make -C realtime

# Check for the successful build of the realtime executable

if [ ! -x "realtime/main" ]; then

echo "Failed to build the realtime executable."

exit 1

fi

# Exiting script

exit 0

```

# software-simulation/shift.sh

```

#!/bin/bash

# Check for arguments

if [ "$#" -ne 3 ]; then

echo "Usage: $0 <shift-amount> <input_file> <output_file>"

exit 1

fi

find_python() {

if command -v python3 &>/dev/null; then

echo "python3"

elif command -v python &>/dev/null; then

echo "python"

else

echo "No suitable Python interpreter found." >&2

exit 1

fi

}

check_scaling_main() {

```

```

echo "realtime/main is not built. Run setup.sh" >&2

exit 1

PYTHON=$(find python)

check scaling main

samples temp="./.samples"

samples scaled temp="./.samples scaled"

# trap 'rm -f "$samples temp" "$samples scaled temp"' EXIT

"$PYTHON" converters/txter.py "$2" "$samples temp"

if [ $? -ne 0 ]; then

exit 1

fi

if ! cat "$samples temp" | realtime/main "$1" > "$samples scaled temp";

then

echo "Scaling failed, exiting." >&2

exit 1

fi

"$PYTHON" converters/waver.py "$samples scaled temp" "$3"

if [ $? -ne 0 ]; then

exit 1

fi

echo "Processing complete."

```

# **Hardware Implementation Files**

#### implementation/hw/components/audio\_piper

```

clk,

reset,

input logic [15:0] left in data,

input logic [15:0] right in data,

right in valid,

right in ready = 0,

left out ready,

output logic [15:0] right out data = 0,

right out valid = 0,

right out ready,

```

```

output logic [9:0] lights = 0

);

logic [15:0] data = 0;

logic [9:0] ctr1 = 0;

logic [9:0] ctr2 = 0;

logic [9:0] ctr3 = 0;

logic [9:0] ctr4 = 0;

logic [9:0] ctr5 = 0;

always_ff @(posedge clk) begin

left_in_ready <= 1;</pre>

if (left_in_ready) begin

if (left out ready) begin

if (right_out_ready) begin

right out data <= data;</pre>

right out valid <= 1;

```

```

if (right_out_valid) begin

right out valid <= 0;

lights[0] <= 1;

lights[0] <= 0;

if (right_in_valid)

lights[1] <= 1;

lights[1] <= 0;

if (left_out_ready)

lights[2] <= 1;

lights[2] <= 0;

if (right_out_ready)

lights[3] <= 1;

lights[3] <= 0;

```

```

ctr3 <= ctr3 + 1;

if (lights[8])

lights[8] <= 0;

else

lights[8] <= 1;

end

else

ctr3 <= ctr3 + 1;

end

endmodule</pre>

```

# implementation/hw/components/cart\_to\_polar

```

module cart_to_polar(

clk,

input logic [15:0] imag_buf_data,

output logic [11:0] imag buf addr = 0,

output logic [15:0] mag buf 0 data = 0,

output logic [11:0] mag buf 0 addr = 0,

mag buf 0 wren = 0,

```

```

output logic [15:0] phase buf 0 data = 0,

output logic [11:0] phase buf 0 addr = 0,

output logic phase buf 0 wren = 0,

output logic [15:0] mag_buf_1 data = 0,

output logic [11:0] mag buf_1_addr = 0,

output logic mag buf 1 wren = 0,

output logic [15:0] phase buf 1 data = 0,

output logic [11:0] phase buf 1 addr = 0,

phase buf 1 wren = 0,

);

logic [15:0] magnitude;

logic [15:0] phase;

logic [11:0] n samples = 0;

logic aux, i ce, done;

topolar polar converter (

.i clk(clk),

.i_reset(!go_in),

.i ce(i ce),

.i xval(real buf data[15:0]),

.i yval(imag buf data[15:0]),

.o mag(magnitude),

.o phase(phase),

.o aux(aux)

```

```

.o done(done)

);

always ff @(posedge clk) begin

if (!going) begin

if (go in) begin

curr buf <= !curr buf;</pre>

real buf addr <= real buf addr + 1;</pre>

imag buf addr <= imag buf addr + 1;</pre>

n samples <= n samples + 1;</pre>

if (!curr buf) begin

mag buf 0 data <= magnitude;</pre>

mag buf 0 addr <= real buf addr - 1;</pre>

mag buf 0 wren <= 1;</pre>

phase buf 0 data <= phase[15:0];</pre>

phase buf 0 addr <= real buf addr - 1;</pre>

phase buf 0 wren <= 1;</pre>

mag buf 1 data <= magnitude;</pre>

mag buf 1 addr <= real buf addr - 1;</pre>

mag buf 1 wren <= 1;</pre>

phase buf 1 data <= phase[15:0];</pre>

phase buf 1 addr <= real buf addr - 1;</pre>

phase buf 1 wren <= 1;</pre>

```

```

if (n samples == 12'd4095) begin

going <= 0;</pre>

end

endmodule

module topolar(i clk, i reset, i ce, i xval, i yval, i aux,

o mag, o phase, o aux);

localparam IW=16, // The number of bits in our inputs

NSTAGES=16,

PW=16; // Bits in our phase variables

i clk, i reset, i ce;

input wire signed [(IW-1):0] i xval, i yval;

output reg signed [(OW-1):0] o_mag;

output reg [(PW-1):0] o phase;

o aux;

```

```

signed [(WW-1):0] e xval, e yval;

assign e xval = { \{(2)\{i xval[(IW-1)]\}\}, i xval, \{(WW-IW-2)\{1'b0\}\}\};

assign e yval = \{ (2) \{ i yval[(IW-1)] \} \}, i yval, \{ (WW-IW-2) \{ 1'b0 \} \} \};

reg signed [(WW-1):0] xv [0:NSTAGES];

reg signed [(WW-1):0] yv [0:NSTAGES];

reg [(PW-1):0] ph [0:NSTAGES];

into

reg [(NSTAGES):0] ax;

always @(posedge i clk)

if (i reset)

ax <= { (NSTAGES+1) {1'b0}};</pre>

ax \le {ax[(NSTAGES-1):0], i aux };

always @(posedge i clk)

if (i reset)

xv[0] <= 0;

yv[0] <= 0;

ph[0] <= 0;

```

```

end else if (i ce)

case({i xval[IW-1], i yval[IW-1]})

2'b01: begin // Rotate by -315 degrees

xv[0] \le e xval - e yval;

yv[0] \le e xval + e yval;

ph[0] <= 19'h70000;

xv[0] \le -e xval + e yval;

yv[0] <= -e xval - e yval;</pre>

ph[0] <= 19'h30000;

xv[0] \leftarrow e yval;

yv[0] <= e_xval - e yval;</pre>

ph[0] <= 19'h50000;

xv[0] \le e xval + e yval;

yv[0] \le -e xval + e yval;

ph[0] <= 19'h10000;

[18:0] cordic angle [0:(NSTAGES-1)];

assign cordic_angle[ 0] = 19'h0_9720; // 26.565051 deg

```

```

assign cordic angle[ 1] = 19'h0 4fd9; // 14.036243 deg

assign cordic angle[ 2] = 19'h0 2888; // 7.125016 deg

assign cordic angle[ 3] = 19'h0 1458; //

assign cordic angle[ 4] = 19'h0 0a2e; // 1.789911 deg

assign cordic angle[ 5] = 19'h0 0517; // 0.895174 deg

assign cordic angle[ 6] = 19'h0 028b; // 0.447614 deg

assign cordic angle[ 7] = 19'h0 0145; // 0.223811 deg

assign cordic angle[ 8] = 19'h0 00a2; // 0.111906 deg

assign cordic angle[ 9] = 19'h0 0051; // 0.055953 deg

assign cordic angle[10] = 19'h0 0028; // 0.027976 deg

assign cordic angle[11] = 19'h0 0014; // 0.013988 deg

assign cordic angle[12] = 19'h0 000a; // 0.006994 deg

assign cordic angle[13] = 19'h0 0005; // 0.003497 deg

assign cordic angle[14] = 19'h0 0002; // 0.001749 deg

assign cordic angle[15] = 19'h0 0001; // 0.000874 deg

genvar i;

generate for(i=0; i<NSTAGES; i=i+1) begin : TOPOLARloop</pre>

always @(posedge i clk)

if (i reset)

xv[i+1] <= 0;

yv[i+1] <= 0;

ph[i+1] <= 0;

if ((cordic angle[i] == 0) | | (i >= WW))

```

```

xv[i+1] \le xv[i];

yv[i+1] \leftarrow yv[i];

ph[i+1] <= ph[i];

end else if (yv[i][(WW-1)]) // Below the axis

xv[i+1] \le xv[i] - (yv[i] >>> (i+1));

yv[i+1] \le yv[i] + (xv[i] >>> (i+1));

ph[i+1] <= ph[i] - cordic_angle[i];</pre>

xv[i+1] \le xv[i] + (yv[i] >>> (i+1));

yv[i+1] \le yv[i] - (xv[i] >>> (i+1));

ph[i+1] <= ph[i] + cordic angle[i];</pre>

if (i == NSTAGES-1) begin

wire

[(WW-1):0] pre mag;

assign pre mag = xv[NSTAGES] + $signed({{(OW)}{1'b0}}),

xv[NSTAGES][(WW-OW)],

{ (WW-OW-1) { !xv[NSTAGES] [WW-OW] } } });

always @(posedge i clk)

```

```

if (i_reset)

begin

o_mag <= 0;

o_phase <= 0;

o_aux <= 0;

end else if (i_ce)

begin

o_mag <= pre_mag[(WW-1):(WW-OW)];

o_phase <= ph[NSTAGES];

o_aux <= ax[NSTAGES];

end

wire    [(WW-OW):0] unused_val;

assign unused_val = { pre_mag[WW-1], pre_mag[(WW-OW-1):0] };

endmodule</pre>

```

## implementation/hw/components/emitter

```

output logic [15:0] right_out_data = 0,

);

logic going = 0;

always_ff @(posedge clk) begin

if (!going) begin

if (go in) begin

going <= 1;</pre>

if (!just finished) begin

tmp <= 1;

out buf

if (tmp) begin

going <= 0;

endmodule

```

## implementation/hw/components/ffter

```

one

module ffter(

input logic clk,

input logic [15:0] in buf data,

output logic [15:0] real buf data = 0,

output logic [11:0] real buf addr = 0,

real buf wren = 0,

output logic [15:0] imag buf data = 0,

output logic [11:0] imag_buf_addr = 0,

imag buf wren = 0,

);

logic going = 0;

```

```

logic just finished = 0;

always_ff @(posedge clk) begin

if (!going) begin

if (go_in) begin

go_out <= 0;</pre>

going <= 1;</pre>

tmp <= 1;

if (tmp) begin

go out <= 1;

going <= 0;

```

# implementation/hw/components/first\_hannifier

```

/*

* Apply Hann Windowing function to a window of samples from the input ring

* buffer

```

```

module first hannifier(

go in,

input logic [15:0] ring buf data,

output logic [12:0] ring_buf_addr = 0, // larger than typical

output logic out buf wren = 0,

);

always ff @(posedge clk) begin

if (!going) begin

if (go in) begin

ring buf addr <= window start;</pre>

```

```

going <= 1;</pre>

if (!just finished) begin

out buf wren <= 1;

out buf data <= ring buf data * hann rom data >> 16; //

hann rom data: Q0.16, I think output is Q16.16, and then take only first

if (ring buf addr == 4095 + 1024) begin

ring_buf_addr <= 0;</pre>

ring buf addr <= ring buf addr + 1;</pre>

going <= 0;

```

## implementation/hw/components/iffter

```

module ffter(

input logic clk,

input logic go in,

input logic [15:0] real buf data,

input logic [15:0] imag buf data,

output logic [11:0] imag buf addr = 0,

output logic [15:0] out buf data = 0,

);

logic going = 0;

```

```

logic just finished = 0;

always_ff @(posedge clk) begin

if (!going) begin

if (go_in) begin

go_out <= 0;</pre>

tmp <= 1;

if (tmp) begin

go out <= 1;

going <= 0;

```

### implementation/hw/components/sampler

```

/*

* Avalon streaming component to read samples of left from_adc channel of

* the Wolfson Audio CODEC to a ring buffer

```

```

module sampler(

input logic clk,

reset,

left in valid,

left in ready = 0,

input logic [15:0] right in data,

right in valid,

right_in_ready = 0,

output logic [15:0] ring buf data,

ring buf wren = 0,

);

logic just finished = 0;

always ff @(posedge clk) begin

if (!going) begin

going <= 1;

```

```

end

out buf

if (tmp) begin

go_out <= 1;</pre>

going <= 0;</pre>

endmodule

```

# implementation/hw/components/scaler

```

input logic [15:0] mag in buf 0 data,

output logic [11:0] mag in buf 0 addr = 0,

input logic [15:0] phase in buf 0 data,

output logic [11:0] phase in buf 0 addr = 0,

input logic [15:0] mag in buf 1 data,

output logic [11:0] mag in buf 1 addr = 0,

input logic [15:0] phase in buf 1 data,

output logic [11:0] phase in buf 1 addr = 0,

input logic [15:0] mag out buf 0 rdata,

output logic [11:0] mag out buf 0 raddr = 0,

output logic [15:0] mag out buf 0 wrdata = 0,

output logic [11:0] mag out buf 0 wraddr = 0,

output logic mag_out_buf_0_wren = 0,

input logic [15:0] phase out buf 0 rdata,

output logic [11:0] phase out buf 0 raddr = 0,

output logic [15:0] phase out buf 0 wrdata = 0,

output logic [11:0] phase out buf 0 wraddr = 0,

output logic phase out buf 0 wren = 0,

input logic [15:0] mag out buf 1 rdata,

output logic [11:0] mag out buf 1 raddr = 0,

```

```

output logic [15:0] mag out buf 1 wrdata = 0,

output logic [11:0] mag out buf 1 wraddr = 0,

output logic mag out buf 1 wren = 0,

input logic [15:0] phase out buf 1 rdata,

output logic [11:0] phase out buf 1 raddr = 0,

output logic [15:0] phase out buf 1 wrdata = 0,

output logic [11:0] phase out buf 1 wraddr = 0,

output logic phase out buf 1 wren = 0,

input logic [15:0] synth mags rdata,

output logic [11:0] synth mags raddr = 0,

output logic [15:0] synth mags wrdata = 0,

output logic [11:0] synth mags wraddr = 0,

output logic synth mags wren = 0,

input logic [15:0] synth devs rdata,

output logic [11:0] synth devs raddr = 0,

output logic [15:0] synth devs wrdata = 0,

output logic [11:0] synth devs wraddr = 0,

output logic synth devs wren = 0,

output logic cur buf = 0,

enum logic [2:0] {awaiting, analysis, synthesis, just finished} state =

awaiting;

logic anal read = 1;

logic cur buf num;

```

```

logic [15:0] mag in data;

logic [15:0] mag in prev data;

logic [15:0] phase in data;

logic [15:0] phase in prev data;

logic [11:0] mag in addr;

logic [11:0] phase in addr;

logic [15:0] mag out rdata;

logic [15:0] mag out prev rdata;

logic [11:0] mag out raddr;

logic [15:0] mag out wrdata;

logic [11:0] mag out wraddr;

mag out wren;

logic [15:0] phase out rdata;

logic [15:0] phase out prev rdata;

logic [11:0] phase out raddr;

logic [11:0] phase out prev raddr;

logic [15:0] phase out wrdata;

logic [11:0] phase out wraddr;

phase out wren;

logic [11:0] i = 0;

logic signed [15:0] d phase;

logic signed [15:0] expected d phase = 0;

logic signed [15:0] d phase from expected;

logic signed [15:0] new bin dev;

logic signed [15:0] fractional bin;

logic signed [31:0] extended mult;

logic signed [15:0] expected d phase increment = 16'h192; // pi/2

logic signed [15:0] bin dev multiplier = 16'h0a3; // 2/pi

logic signed [15:0] pi = 16'h324;

logic signed [15:0] two pi = 16'h648;

logic signed [15:0] neg pi = 16'h9b8;

```

```

mag_in_data = cur_buf_num ? mag_in_buf_1_data : mag_in_buf_0_data;

mag in prev data = cur buf num ? mag in buf 0 data :

mag_in_buf_1_data;

mag_in_buf_0_addr = mag_in_addr;

mag in buf 1 addr = mag in addr;

phase in data = cur buf num ? phase in buf 1 data :

phase_in_buf_0_data;

phase_in_prev_data = cur_buf_num ? phase_in_buf_0_data :

phase in buf 1 data;

phase in buf 0 addr = phase in addr;

phase_in_buf_1_addr = phase_in_addr;

mag out rdata = cur buf num ? mag out buf 1 rdata :

mag out buf 0 rdata;

mag out prev rdata = cur buf num ? mag out buf 0 rdata :

mag_out_buf_1_rdata;

mag out buf 0 raddr = mag out raddr;

mag out buf 1 raddr = mag out raddr;

mag out buf 0 wraddr = mag out wraddr;

mag out buf 1 wraddr = mag out wraddr;

mag_out_buf_0_wrdata = mag_out_wrdata;

mag out buf 1 wrdata = mag out wrdata;

mag_out_buf_0_wren = mag_out_wren && !cur_buf_num;

mag out buf 1 wren = mag out wren && cur buf num;

phase out rdata = cur buf num ? phase out buf 1 rdata :

phase_out_buf_0_rdata;

phase out prev rdata = cur buf num ? phase out buf 0 rdata:

phase_out_buf_1_rdata;

phase out buf 0 raddr = phase out raddr;

phase out buf 1 raddr = phase out raddr;

phase_out_buf_0_wraddr = phase_out_wraddr;

```

```

phase out buf 1 wraddr = phase out wraddr;

phase out buf 0 wrdata = phase out wrdata;

phase out buf 1 wrdata = phase out wrdata;

phase out buf 0 wren = phase out wren && !cur buf num;

phase out buf 1 wren = phase out wren && cur buf num;

always ff @(posedge clk) begin

case (state)

if (go_in) begin

go_out <= 0;

cur buf num <= cur window; // gets set at go, stays for</pre>

state <= analysis;</pre>

expected d phase <= 0;</pre>

anal read <= 1;</pre>

analysis: begin

d_phase = phase_in_data - phase_in_prev_data;

if (d phase < 0) d phase = d phase + two pi; // wrap from 0</pre>

d phase from expected = d phase - expected d phase;

if (d_phase_from_expected < neg_pi) d_phase_from_expected =</pre>

d phase from expected + two pi; // wrap from -pi to pi

bin dev = d phase from expected * bin dev multiplier;

if (extended mult > (2047 << 16)) // above Nyquist

```

```

new bin = extended mult >> 16;

if (new bin[7]) new bin num = new bin num + (2 ** 8); // if

most significant fractional bit is 1, round up

synth mags raddr = new bin num >> 8;

synth devs raddr = new bin num >> 8;

synth mags wren = 0;

synth devs wren = 0;

synth mags wrdata <= synth mags rdata + mag in data;</pre>

synth devs wrdata <= synth devs rdata + new bin dev;</pre>

synth mags wraddr <= new bin num >> 8;

synth devs wraddr <= new bin num >> 8;

synth mags wren <= 1;</pre>

synth devs wren <= 1;</pre>

i \le (i == 2048) ? 0 : i + 1;

expected d phase <= expected d phase +</pre>

expected d phase increment;

if (i == 2048) begin

state <= synthesis;</pre>

synth mags wren <= 0;</pre>

synth devs wren <= 0;</pre>

synth mags raddr <= 0;</pre>

synth devs raddr <= 0;</pre>

synth mags wrdata <= 0;</pre>

synth devs wrdata <= 0;</pre>

synth mags raddr <= 0;</pre>

phase out prev raddr <= 0;</pre>

expected d phase <= 0;</pre>

```

```

anal read <= 1;</pre>

phase out wrdata <= phase out prev rdata + expected d phase;</pre>